16-लेयर पीसीबी आधुनिक इलेक्ट्रॉनिक उपकरणांसाठी आवश्यक असलेली जटिलता आणि लवचिकता प्रदान करतात. कुशल डिझाइन आणि स्टॅकिंग अनुक्रमांची निवड आणि इंटरलेअर कनेक्शन पद्धती इष्टतम बोर्ड कार्यप्रदर्शन साध्य करण्यासाठी महत्त्वपूर्ण आहेत. या लेखात, आम्ही डिझाइनर आणि अभियंत्यांना कार्यक्षम आणि विश्वासार्ह 16-लेयर सर्किट बोर्ड तयार करण्यात मदत करण्यासाठी विचार, मार्गदर्शक तत्त्वे आणि सर्वोत्तम पद्धतींचा शोध घेऊ.

1.16 लेयर PCBs स्टॅकिंग सिक्वेन्सची मूलभूत माहिती समजून घेणे

1.1 स्टॅकिंग ऑर्डरची व्याख्या आणि उद्देश

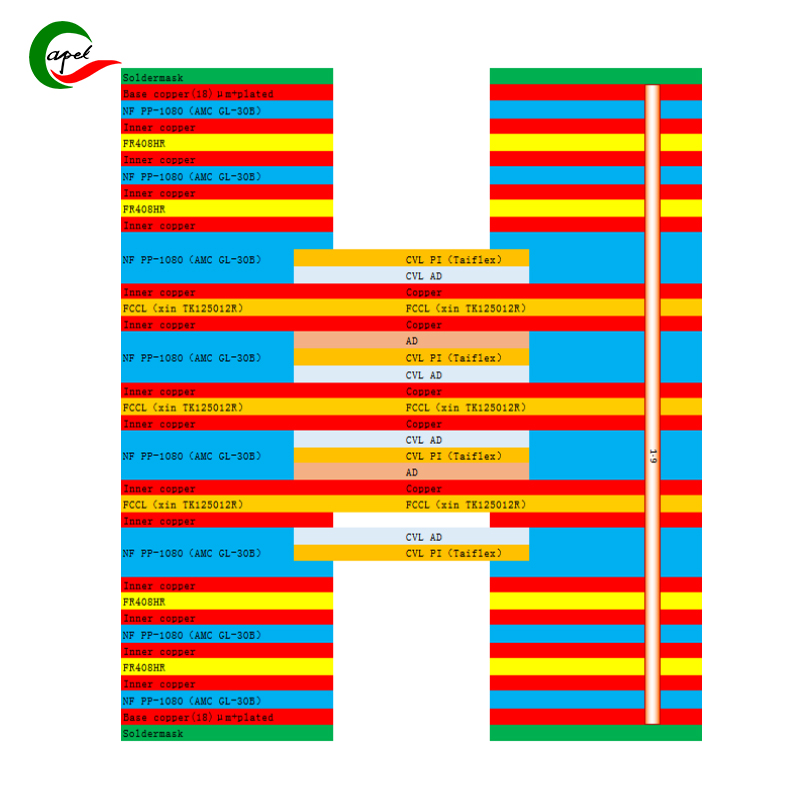

स्टॅकिंग क्रम म्हणजे व्यवस्था आणि क्रम ज्यामध्ये तांबे आणि इन्सुलेटिंग लेयर्स सारख्या सामग्रीचे लॅमिनेशन करून मल्टी-लेयर सर्किट बोर्ड तयार केले जाते. स्टॅकिंग क्रम सिग्नल लेयर्स, पॉवर लेयर्स, ग्राउंड लेयर आणि इतर महत्वाचे घटकांचे स्थान निश्चित करतो. स्टॅक.

स्टॅकिंग क्रमाचा मुख्य उद्देश बोर्डची आवश्यक विद्युत आणि यांत्रिक गुणधर्म प्राप्त करणे आहे. सर्किट बोर्डचा प्रतिबाधा, सिग्नल अखंडता, वीज वितरण, थर्मल व्यवस्थापन आणि उत्पादन व्यवहार्यता निश्चित करण्यात ती महत्त्वाची भूमिका बजावते. स्टॅकिंग क्रम बोर्डच्या एकूण कार्यक्षमतेवर, विश्वासार्हतेवर आणि उत्पादनक्षमतेवर देखील परिणाम करतो.

1.2 स्टॅकिंग सीक्वेन्स डिझाइनवर परिणाम करणारे घटक: स्टॅकिंग सिक्वेन्स डिझाइन करताना अनेक घटकांचा विचार केला पाहिजे

16-लेयर पीसीबी:

अ) विद्युत विचार:सिग्नल, पॉवर आणि ग्राउंड प्लेनचे लेआउट योग्य सिग्नल अखंडता, प्रतिबाधा नियंत्रण आणि इलेक्ट्रोमॅग्नेटिक हस्तक्षेप कमी करणे सुनिश्चित करण्यासाठी ऑप्टिमाइझ केले पाहिजे.

ब) थर्मल विचार:पॉवर आणि ग्राउंड प्लेनची नियुक्ती आणि थर्मल व्हियाचा समावेश उष्णता प्रभावीपणे नष्ट करण्यास आणि घटकाचे इष्टतम ऑपरेटिंग तापमान राखण्यास मदत करते.

c) उत्पादन मर्यादा:निवडलेल्या स्टॅकिंग क्रमाने PCB उत्पादन प्रक्रियेच्या क्षमता आणि मर्यादा विचारात घेतल्या पाहिजेत, जसे की सामग्रीची उपलब्धता, स्तरांची संख्या, ड्रिल आस्पेक्ट रेशो,आणि संरेखन अचूकता.

ड) खर्च ऑप्टिमायझेशन:आवश्यक कामगिरी आणि विश्वासार्हता सुनिश्चित करताना सामग्रीची निवड, स्तरांची संख्या आणि स्टॅक-अप जटिलता प्रकल्पाच्या बजेटशी सुसंगत असावी.

1.3 16-लेयर सर्किट बोर्ड स्टॅकिंग अनुक्रमांचे सामान्य प्रकार: 16-लेयरसाठी अनेक सामान्य स्टॅकिंग अनुक्रम आहेत

पीसीबी, इच्छित कामगिरी आणि आवश्यकतांवर अवलंबून. काही सामान्य उदाहरणे समाविष्ट आहेत:

अ) सममितीय स्टॅकिंग क्रम:या क्रमामध्ये चांगली सिग्नल अखंडता, किमान क्रॉसस्टॉक आणि संतुलित उष्णता नष्ट होण्यासाठी पॉवर आणि ग्राउंड लेयरमध्ये सममितीयपणे सिग्नल स्तर ठेवणे समाविष्ट आहे.

b) अनुक्रमिक स्टॅकिंग क्रम:या क्रमामध्ये, सिग्नल स्तर पॉवर आणि ग्राउंड लेयर्स दरम्यान अनुक्रमे असतात. हे लेयर व्यवस्थेवर अधिक नियंत्रण प्रदान करते आणि विशिष्ट सिग्नल अखंडतेच्या आवश्यकता पूर्ण करण्यासाठी फायदेशीर आहे.

c) मिश्रित स्टॅकिंग ऑर्डर:यामध्ये सममितीय आणि अनुक्रमिक स्टॅकिंग ऑर्डरचे संयोजन समाविष्ट आहे. हे बोर्डच्या विशिष्ट भागांसाठी लेअपचे सानुकूलित आणि ऑप्टिमायझेशन करण्यास अनुमती देते.

ड) सिग्नल-संवेदनशील स्टॅकिंग क्रम:हा क्रम अधिक चांगल्या आवाजाची प्रतिकारशक्ती आणि अलगावसाठी संवेदनशील सिग्नल स्तर जमिनीच्या समतल जवळ ठेवतो.

2. 16 लेयर पीसीबी स्टॅकिंग सीक्वेन्स सिलेक्शनसाठी मुख्य विचार:

2.1 सिग्नलची अखंडता आणि उर्जा अखंडता विचार:

स्टॅकिंग क्रम बोर्डच्या सिग्नल अखंडतेवर आणि पॉवर अखंडतेवर महत्त्वपूर्ण प्रभाव पाडतो. सिग्नलची विकृती, आवाज आणि इलेक्ट्रोमॅग्नेटिक हस्तक्षेपाचा धोका कमी करण्यासाठी सिग्नल आणि पॉवर/ग्राउंड प्लेनचे योग्य प्लेसमेंट महत्त्वपूर्ण आहे. मुख्य विचारांमध्ये हे समाविष्ट आहे:

अ) सिग्नल लेयर प्लेसमेंट:कमी इंडक्टन्स रिटर्न पथ प्रदान करण्यासाठी आणि आवाज जोडणी कमी करण्यासाठी हाय-स्पीड सिग्नल स्तर जमिनीच्या समतलाजवळ ठेवले पाहिजेत. सिग्नल स्क्यू आणि लांबी जुळणी कमी करण्यासाठी सिग्नल स्तर देखील काळजीपूर्वक तयार केले पाहिजेत.

b) पॉवर प्लेन वितरण:स्टॅकिंग अनुक्रमाने पॉवर अखंडतेला समर्थन देण्यासाठी पुरेसे पॉवर प्लेन वितरण सुनिश्चित केले पाहिजे. व्होल्टेज थेंब, प्रतिबाधा खंडित होणे आणि आवाज जोडणे कमी करण्यासाठी पुरेसे पॉवर आणि ग्राउंड प्लेन धोरणात्मकपणे ठेवले पाहिजेत.

c) डिकपलिंग कॅपेसिटर:पुरेसे पॉवर ट्रान्सफर सुनिश्चित करण्यासाठी आणि वीज पुरवठ्याचा आवाज कमी करण्यासाठी डिकपलिंग कॅपेसिटरचे योग्य प्लेसमेंट महत्त्वपूर्ण आहे. स्टॅकिंग अनुक्रमाने पॉवर आणि ग्राउंड प्लेनमध्ये डीकपलिंग कॅपेसिटरची समीपता आणि समीपता प्रदान केली पाहिजे.

2.2 थर्मल व्यवस्थापन आणि उष्णता नष्ट होणे:

सर्किट बोर्डची विश्वासार्हता आणि कार्यप्रदर्शन सुनिश्चित करण्यासाठी कार्यक्षम थर्मल व्यवस्थापन महत्त्वपूर्ण आहे. स्टॅकिंग क्रमाने पॉवर आणि ग्राउंड प्लेन, थर्मल व्हिया आणि इतर शीतकरण यंत्रणांचे योग्य स्थान विचारात घेतले पाहिजे. महत्त्वपूर्ण विचारांमध्ये हे समाविष्ट आहे:

अ) पॉवर प्लेन वितरण:संपूर्ण स्टॅकमध्ये पॉवर आणि ग्राउंड प्लेनचे पुरेसे वितरण संवेदनशील घटकांपासून थेट उष्णता दूर करण्यास मदत करते आणि संपूर्ण बोर्डवर समान तापमान वितरण सुनिश्चित करते.

b) थर्मल मार्ग:स्टॅकिंग सीक्वेन्सने आतील थरातून बाहेरील थर किंवा उष्मा सिंकपर्यंत उष्णता नष्ट करणे सुलभ करण्यासाठी प्लेसमेंटद्वारे प्रभावी थर्मलची अनुमती दिली पाहिजे. हे स्थानिकीकृत हॉट स्पॉट्स टाळण्यास मदत करते आणि कार्यक्षम उष्णता नष्ट करणे सुनिश्चित करते.

c) घटक प्लेसमेंट:स्टॅकिंग अनुक्रमाने ओव्हरहाटिंग टाळण्यासाठी हीटिंग घटकांची व्यवस्था आणि समीपतेचा विचार केला पाहिजे. उष्णता सिंक किंवा पंखे यांसारख्या कूलिंग यंत्रणेसह घटकांचे योग्य संरेखन देखील विचारात घेतले पाहिजे.

2.3 उत्पादन मर्यादा आणि खर्च ऑप्टिमायझेशन:

स्टॅकिंग क्रमाने मॅन्युफॅक्चरिंग मर्यादा आणि खर्च ऑप्टिमायझेशन लक्षात घेतले पाहिजे कारण ते बोर्डच्या व्यवहार्यता आणि परवडण्यामध्ये महत्त्वाची भूमिका बजावतात. विचारांमध्ये हे समाविष्ट आहे:

अ) साहित्याची उपलब्धता:निवडलेला स्टॅकिंग क्रम सामग्रीची उपलब्धता आणि निवडलेल्या PCB उत्पादन प्रक्रियेशी त्यांची सुसंगतता यांच्याशी सुसंगत असावा.

b) स्तरांची संख्या आणि जटिलता:स्टॅकिंग क्रम निवडलेल्या PCB उत्पादन प्रक्रियेच्या मर्यादांमध्ये, स्तरांची संख्या, ड्रिल आस्पेक्ट रेशो आणि संरेखन अचूकता यासारख्या घटकांचा विचार करून डिझाइन केले जावे.

c) खर्च ऑप्टिमायझेशन:स्टॅकिंग क्रमाने आवश्यक कार्यप्रदर्शन आणि विश्वासार्हतेशी तडजोड न करता सामग्रीचा वापर ऑप्टिमाइझ केला पाहिजे आणि उत्पादनाची जटिलता कमी केली पाहिजे. भौतिक कचरा, प्रक्रियेची जटिलता आणि असेंबलीशी संबंधित खर्च कमी करणे हे त्याचे उद्दिष्ट असावे.

2.4 स्तर संरेखन आणि सिग्नल क्रॉसस्टॉक:

स्टॅकिंग क्रमाने स्तर संरेखन समस्यांचे निराकरण केले पाहिजे आणि सिग्नलच्या अखंडतेवर नकारात्मक परिणाम करणारे सिग्नल क्रॉसस्टॉक कमी केले पाहिजे. महत्त्वपूर्ण विचारांमध्ये हे समाविष्ट आहे:

अ) सममितीय स्टॅकिंग:पॉवर आणि ग्राउंड लेयर्समधील सिग्नल लेयर्सचे सममितीय स्टॅकिंग कपलिंग कमी करण्यात आणि क्रॉसस्टॉक कमी करण्यात मदत करते.

b) विभेदक जोडी राउटिंग:स्टॅकिंग क्रमाने हाय-स्पीड डिफरेंशियल सिग्नलच्या कार्यक्षम मार्गासाठी सिग्नल स्तरांना योग्यरित्या संरेखित केले पाहिजे. हे सिग्नलची अखंडता राखण्यात आणि क्रॉसस्टॉक कमी करण्यात मदत करते.

c) सिग्नल वेगळे करणे:क्रॉसस्टॉक आणि हस्तक्षेप कमी करण्यासाठी स्टॅकिंग क्रमाने संवेदनशील ॲनालॉग आणि डिजिटल सिग्नल वेगळे करण्याचा विचार केला पाहिजे.

2.5 प्रतिबाधा नियंत्रण आणि RF/मायक्रोवेव्ह एकत्रीकरण:

RF/मायक्रोवेव्ह ऍप्लिकेशन्ससाठी, योग्य प्रतिबाधा नियंत्रण आणि एकीकरण साध्य करण्यासाठी स्टॅकिंग अनुक्रम महत्त्वपूर्ण आहे. मुख्य विचारांमध्ये हे समाविष्ट आहे:

अ) नियंत्रित प्रतिबाधा:स्टॅकिंग क्रमाने ट्रेस रुंदी, डायलेक्ट्रिक जाडी आणि लेयर व्यवस्था यासारख्या घटकांचा विचार करून नियंत्रित प्रतिबाधा डिझाइनसाठी परवानगी दिली पाहिजे. हे RF/मायक्रोवेव्ह सिग्नलसाठी योग्य सिग्नल प्रसार आणि प्रतिबाधा जुळणी सुनिश्चित करते.

b) सिग्नल लेयर प्लेसमेंट:आरएफ/मायक्रोवेव्ह सिग्नल इतर सिग्नल्समधील हस्तक्षेप कमी करण्यासाठी आणि सिग्नलचा चांगला प्रसार प्रदान करण्यासाठी बाह्य स्तराजवळ धोरणात्मकरित्या ठेवले पाहिजे.

c) आरएफ शील्डिंग:स्टॅकिंग क्रमामध्ये RF/मायक्रोवेव्ह सिग्नलला हस्तक्षेपापासून वेगळे करण्यासाठी आणि संरक्षित करण्यासाठी जमिनीवर आणि शिल्डिंग लेयर्सचे योग्य स्थान समाविष्ट असावे.

3.इंटरलेअर कनेक्शन पद्धती

3.1 छिद्र, आंधळे छिद्र आणि पुरलेल्या छिद्रांद्वारे:

विविध स्तरांना जोडण्याचे साधन म्हणून मुद्रित सर्किट बोर्ड (पीसीबी) डिझाइनमध्ये विआचा मोठ्या प्रमाणावर वापर केला जातो. ते पीसीबीच्या सर्व थरांमधून छिद्रे पाडतात आणि विद्युत सातत्य प्रदान करण्यासाठी प्लेट केलेले असतात. छिद्रांद्वारे मजबूत विद्युत कनेक्शन मिळते आणि ते बनवणे आणि दुरुस्त करणे तुलनेने सोपे असते. तथापि, त्यांना मोठ्या ड्रिल बिट आकारांची आवश्यकता असते, जे PCB वर मौल्यवान जागा घेतात आणि राउटिंग पर्याय मर्यादित करतात.

आंधळे आणि दफन केलेल्या विया या पर्यायी इंटरलेअर कनेक्शन पद्धती आहेत ज्या जागा वापर आणि राउटिंग लवचिकतेमध्ये फायदे देतात.

ब्लाइंड वियास पीसीबीच्या पृष्ठभागावरून ड्रिल केले जातात आणि सर्व स्तरांमधून न जाता आतील थरांमध्ये संपतात. खोल थरांना अप्रभावित ठेवताना ते समीप स्तरांमधील कनेक्शनला परवानगी देतात. हे बोर्डच्या जागेचा अधिक कार्यक्षम वापर करण्यास अनुमती देते आणि ड्रिल छिद्रांची संख्या कमी करते. दुस-या बाजूला, दफन केलेले वियास हे छिद्र आहेत जे पीसीबीच्या आतील थरांमध्ये पूर्णपणे बंद आहेत आणि बाहेरील थरांपर्यंत विस्तारत नाहीत. ते बाह्य स्तरांवर परिणाम न करता आतील स्तरांमधील कनेक्शन प्रदान करतात. थ्रू-होल आणि ब्लाइंड व्हियाच्या तुलनेत पुरलेल्या वायसचे जास्त जागा-बचत फायदे आहेत कारण ते बाहेरील थरात कोणतीही जागा घेत नाहीत.

थ्रू होल, ब्लाइंड व्हिया आणि बरीड व्हियाची निवड पीसीबी डिझाइनच्या विशिष्ट आवश्यकतांवर अवलंबून असते. थ्रू होल्स सामान्यत: सोप्या डिझाइनमध्ये वापरले जातात किंवा जिथे मजबूती आणि दुरुस्तीची क्षमता ही प्राथमिक चिंता असते. उच्च-घनतेच्या डिझाइनमध्ये जिथे जागा हा एक महत्त्वाचा घटक आहे, जसे की हँडहेल्ड डिव्हाइसेस, स्मार्टफोन आणि लॅपटॉप, अंध आणि दफन केलेल्या वियास प्राधान्य दिले जाते.

3.2 मायक्रोपोर आणिएचडीआय तंत्रज्ञान:

मायक्रोव्हिया हे लहान व्यासाचे छिद्र असतात (सामान्यत: 150 मायक्रॉनपेक्षा कमी) जे PCB मध्ये उच्च-घनता इंटरलेअर कनेक्शन प्रदान करतात. ते लघुकरण, सिग्नल अखंडता आणि राउटिंग लवचिकता मध्ये महत्त्वपूर्ण फायदे देतात.

मायक्रोव्हियास दोन प्रकारात विभागले जाऊ शकतात: थ्रू-होल मायक्रोव्हिया आणि ब्लाइंड मायक्रोव्हिया. मायक्रोव्हिया पीसीबीच्या वरच्या पृष्ठभागावर छिद्र पाडून आणि सर्व स्तरांमधून विस्तारित करून तयार केले जातात. ब्लाइंड मायक्रोव्हिया, नावाप्रमाणेच, केवळ विशिष्ट अंतर्गत स्तरांपर्यंत विस्तारित आहे आणि सर्व स्तरांमध्ये प्रवेश करू नका.

उच्च घनता इंटरकनेक्ट (HDI) हे एक तंत्रज्ञान आहे जे उच्च सर्किट घनता आणि कार्यप्रदर्शन प्राप्त करण्यासाठी मायक्रोव्हिया आणि प्रगत उत्पादन तंत्र वापरते. एचडीआय तंत्रज्ञान लहान घटकांच्या प्लेसमेंटसाठी आणि कडक राउटिंगसाठी परवानगी देते, परिणामी लहान फॉर्म घटक आणि उच्च सिग्नल अखंडता. एचडीआय तंत्रज्ञान हे लघुकरण, सुधारित सिग्नल प्रसार, कमी सिग्नल विकृती आणि वर्धित कार्यक्षमतेच्या दृष्टीने पारंपारिक पीसीबी तंत्रज्ञानापेक्षा अनेक फायदे देते. हे एकाधिक मायक्रोव्हियासह बहुस्तरीय डिझाइनना अनुमती देते, ज्यामुळे इंटरकनेक्ट लांबी कमी होते आणि परजीवी कॅपेसिटन्स आणि इंडक्टन्स कमी होते.

एचडीआय तंत्रज्ञान उच्च-फ्रिक्वेंसी लॅमिनेट आणि पातळ डायलेक्ट्रिक थर यांसारख्या प्रगत सामग्रीचा वापर करण्यास सक्षम करते, जे RF/मायक्रोवेव्ह अनुप्रयोगांसाठी महत्त्वपूर्ण आहेत. हे उत्तम प्रतिबाधा नियंत्रण प्रदान करते, सिग्नलचे नुकसान कमी करते आणि विश्वसनीय हाय-स्पीड सिग्नल ट्रान्समिशन सुनिश्चित करते.

3.3 इंटरलेअर कनेक्शन साहित्य आणि प्रक्रिया:

पीसीबीची चांगली विद्युत कार्यक्षमता, यांत्रिक विश्वासार्हता आणि उत्पादनक्षमता सुनिश्चित करण्यासाठी इंटरलेअर कनेक्शन सामग्री आणि तंत्रांची निवड महत्त्वपूर्ण आहे. काही सामान्यतः वापरल्या जाणाऱ्या इंटरलेअर कनेक्शन सामग्री आणि तंत्रे आहेत:

अ) तांबे:उत्कृष्ट चालकता आणि सोल्डरबिलिटीमुळे तांबे पीसीबीच्या प्रवाहकीय स्तरांमध्ये आणि वियामध्ये मोठ्या प्रमाणावर वापरले जाते. विश्वासार्ह विद्युत कनेक्शन प्रदान करण्यासाठी ते सामान्यतः छिद्रावर लावले जाते.

b) सोल्डरिंग:सोल्डरिंग तंत्र, जसे की वेव्ह सोल्डरिंग किंवा रीफ्लो सोल्डरिंग, बहुतेकदा PCB आणि इतर घटकांवरील छिद्रांद्वारे विद्युत जोडणी करण्यासाठी वापरली जातात. व्हायावर सोल्डर पेस्ट लावा आणि सोल्डर वितळण्यासाठी उष्णता लागू करा आणि एक विश्वासार्ह कनेक्शन तयार करा.

c) इलेक्ट्रोप्लेटिंग:इलेक्ट्रोप्लेटिंग तंत्र जसे की इलेक्ट्रोलेस कॉपर प्लेटिंग किंवा इलेक्ट्रोलाइटिक कॉपर प्लेट विअसमध्ये चालकता वाढविण्यासाठी आणि चांगले विद्युत कनेक्शन सुनिश्चित करण्यासाठी वापरले जातात.

ड) बाँडिंग:बाँडिंग तंत्र, जसे की चिकट बाँडिंग किंवा थर्मोकंप्रेशन बाँडिंग, स्तरित संरचना एकत्र जोडण्यासाठी आणि विश्वासार्ह इंटरकनेक्शन तयार करण्यासाठी वापरली जातात.

e) डायलेक्ट्रिक सामग्री:पीसीबी स्टॅकअपसाठी डायलेक्ट्रिक सामग्रीची निवड इंटरलेअर कनेक्शनसाठी महत्त्वपूर्ण आहे. उच्च वारंवारता लॅमिनेट जसे की FR-4 किंवा रॉजर्स लॅमिनेट बहुतेक वेळा चांगली सिग्नल अखंडता सुनिश्चित करण्यासाठी आणि सिग्नलचे नुकसान कमी करण्यासाठी वापरले जातात.

3.4 क्रॉस-सेक्शनल डिझाइन आणि अर्थ:

पीसीबी स्टॅकअपचे क्रॉस-सेक्शनल डिझाइन लेयर्समधील कनेक्शनचे इलेक्ट्रिकल आणि यांत्रिक गुणधर्म निर्धारित करते. क्रॉस-सेक्शन डिझाइनसाठी मुख्य विचारांमध्ये हे समाविष्ट आहे:

अ) थर व्यवस्था:PCB स्टॅकअपमध्ये सिग्नल, पॉवर आणि ग्राउंड प्लेनची व्यवस्था सिग्नल अखंडता, पॉवर इंटिग्रिटी आणि इलेक्ट्रोमॅग्नेटिक इंटरफेरन्स (EMI) प्रभावित करते. पॉवर आणि ग्राउंड प्लेनसह सिग्नल स्तरांचे योग्य प्लेसमेंट आणि संरेखन आवाज जोडणी कमी करण्यास आणि कमी इंडक्टन्स रिटर्न पथ सुनिश्चित करण्यात मदत करते.

b) प्रतिबाधा नियंत्रण:क्रॉस-सेक्शन डिझाइनने नियंत्रित प्रतिबाधा आवश्यकता विचारात घेतल्या पाहिजेत, विशेषत: हाय-स्पीड डिजिटल किंवा RF/मायक्रोवेव्ह सिग्नलसाठी. यामध्ये इच्छित वैशिष्ट्यपूर्ण प्रतिबाधा साध्य करण्यासाठी डायलेक्ट्रिक सामग्री आणि जाडीची योग्य निवड समाविष्ट आहे.

c) थर्मल व्यवस्थापन:क्रॉस-सेक्शन डिझाइनमध्ये प्रभावी उष्णता नष्ट करणे आणि थर्मल व्यवस्थापनाचा विचार केला पाहिजे. पॉवर आणि ग्राउंड प्लेन, थर्मल व्हिया आणि कूलिंग मेकॅनिझमसह घटक (जसे की हीट सिंक) योग्य प्लेसमेंट उष्णता नष्ट करण्यास आणि इष्टतम ऑपरेटिंग तापमान राखण्यास मदत करतात.

ड) यांत्रिक विश्वसनीयता:सेक्शन डिझाइनमध्ये यांत्रिक विश्वासार्हतेचा विचार केला पाहिजे, विशेषत: थर्मल सायकलिंग किंवा यांत्रिक तणावाच्या अधीन असलेल्या अनुप्रयोगांमध्ये. सामग्रीची योग्य निवड, बाँडिंग तंत्र आणि स्टॅकअप कॉन्फिगरेशन पीसीबीची संरचनात्मक अखंडता आणि टिकाऊपणा सुनिश्चित करण्यात मदत करते.

4.16-लेयर पीसीबीसाठी डिझाइन मार्गदर्शक तत्त्वे

4.1 स्तर वाटप आणि वितरण:

16-लेयर सर्किट बोर्ड डिझाइन करताना, कार्यप्रदर्शन आणि सिग्नल अखंडता ऑप्टिमाइझ करण्यासाठी लेयरचे काळजीपूर्वक वाटप आणि वितरण करणे महत्वाचे आहे. टियर वाटपासाठी येथे काही मार्गदर्शक तत्त्वे आहेत

आणि वितरण:

आवश्यक सिग्नल स्तरांची संख्या निश्चित करा:

सर्किट डिझाइनची जटिलता आणि रूट करणे आवश्यक असलेल्या सिग्नलची संख्या विचारात घ्या. सर्व आवश्यक सिग्नल सामावून घेण्यासाठी पुरेशा सिग्नल स्तरांचे वाटप करा, पुरेशी राउटिंग जागा सुनिश्चित करा आणि अतिरेक टाळागर्दी ग्राउंड आणि पॉवर प्लेन नियुक्त करा:

जमिनीवर आणि पॉवर प्लेनला किमान दोन आतील स्तर नियुक्त करा. ग्राउंड प्लेन सिग्नलसाठी स्थिर संदर्भ प्रदान करण्यात मदत करते आणि इलेक्ट्रोमॅग्नेटिक हस्तक्षेप (EMI) कमी करते. पॉवर प्लेन कमी-प्रतिबाधा वीज वितरण नेटवर्क प्रदान करते जे व्होल्टेज थेंब कमी करण्यास मदत करते.

वेगळे संवेदनशील सिग्नल स्तर:

अनुप्रयोगावर अवलंबून, हस्तक्षेप आणि क्रॉसस्टॉक टाळण्यासाठी संवेदनशील किंवा उच्च-गती सिग्नल स्तर गोंगाट किंवा उच्च-शक्तीच्या स्तरांपासून वेगळे करणे आवश्यक असू शकते. हे त्यांच्या दरम्यान समर्पित ग्राउंड किंवा पॉवर प्लेन ठेवून किंवा अलगाव स्तर वापरून केले जाऊ शकते.

सिग्नल स्तर समान रीतीने वितरित करा:

समीप सिग्नलमधील कपलिंग कमी करण्यासाठी आणि सिग्नलची अखंडता राखण्यासाठी संपूर्ण बोर्ड स्टॅकअपमध्ये सिग्नल स्तर समान रीतीने वितरित करा. इंटरलेअर क्रॉसस्टॉक कमी करण्यासाठी समान स्टॅकअप क्षेत्रात सिग्नल लेयर एकमेकांच्या पुढे ठेवणे टाळा.

उच्च-फ्रिक्वेंसी सिग्नलचा विचार करा:

तुमच्या डिझाइनमध्ये उच्च-फ्रिक्वेंसी सिग्नल असल्यास, ट्रान्समिशन लाइन इफेक्ट्स कमी करण्यासाठी आणि प्रसार विलंब कमी करण्यासाठी उच्च-फ्रिक्वेंसी सिग्नल स्तर बाह्य स्तरांच्या जवळ ठेवण्याचा विचार करा.

4.2 रूटिंग आणि सिग्नल राउटिंग:

राउटिंग आणि सिग्नल ट्रेस डिझाइन योग्य सिग्नल अखंडता सुनिश्चित करण्यासाठी आणि हस्तक्षेप कमी करण्यासाठी महत्त्वपूर्ण आहेत. 16-लेयर सर्किट बोर्डवर लेआउट आणि सिग्नल रूटिंगसाठी येथे काही मार्गदर्शक तत्त्वे आहेत:

उच्च-वर्तमान सिग्नलसाठी विस्तृत ट्रेस वापरा:

पॉवर आणि ग्राउंड कनेक्शन यांसारख्या उच्च प्रवाह असलेल्या सिग्नलसाठी, प्रतिकार आणि व्होल्टेज ड्रॉप कमी करण्यासाठी विस्तृत ट्रेस वापरा.

हाय-स्पीड सिग्नलसाठी जुळणारे प्रतिबाधा:

हाय-स्पीड सिग्नलसाठी, परावर्तन आणि सिग्नल क्षीण होणे टाळण्यासाठी ट्रेस प्रतिबाधा ट्रान्समिशन लाइनच्या वैशिष्ट्यपूर्ण प्रतिबाधाशी जुळत असल्याची खात्री करा. नियंत्रित प्रतिबाधा डिझाइन तंत्र वापरा आणि अचूक ट्रेस रुंदीची गणना करा.

ट्रेस लांबी आणि क्रॉसओव्हर पॉइंट्स कमी करा:

ट्रेस लांबी शक्य तितक्या लहान ठेवा आणि परजीवी कॅपेसिटन्स, इंडक्टन्स आणि हस्तक्षेप कमी करण्यासाठी क्रॉसओव्हर पॉइंट्सची संख्या कमी करा. घटक प्लेसमेंट ऑप्टिमाइझ करा आणि लांब, जटिल ट्रेस टाळण्यासाठी समर्पित राउटिंग स्तर वापरा.

हाय-स्पीड आणि लो-स्पीड सिग्नल वेगळे करा:

हाय-स्पीड सिग्नलवर आवाजाचा प्रभाव कमी करण्यासाठी हाय-स्पीड आणि लो-स्पीड सिग्नल वेगळे करा. समर्पित सिग्नल स्तरांवर हाय-स्पीड सिग्नल ठेवा आणि त्यांना उच्च-शक्ती किंवा गोंगाट करणाऱ्या घटकांपासून दूर ठेवा.

हाय-स्पीड सिग्नलसाठी विभेदक जोड्या वापरा:

आवाज कमी करण्यासाठी आणि हाय-स्पीड डिफरेंशियल सिग्नलसाठी सिग्नलची अखंडता राखण्यासाठी, विभेदक जोडी राउटिंग तंत्र वापरा. सिग्नल स्क्यू आणि क्रॉसस्टॉक टाळण्यासाठी विभेदक जोड्यांची प्रतिबाधा आणि लांबी जुळत ठेवा.

4.3 ग्राउंड लेयर आणि पॉवर लेयर वितरण:

चांगली उर्जा अखंडता प्राप्त करण्यासाठी आणि इलेक्ट्रोमॅग्नेटिक हस्तक्षेप कमी करण्यासाठी ग्राउंड आणि पॉवर प्लेनचे योग्य वितरण महत्त्वपूर्ण आहे. 16-लेयर सर्किट बोर्डांवर ग्राउंड आणि पॉवर प्लेन असाइनमेंटसाठी येथे काही मार्गदर्शक तत्त्वे आहेत:

समर्पित ग्राउंड आणि पॉवर प्लेन वाटप करा:

समर्पित ग्राउंड आणि पॉवर प्लेनसाठी किमान दोन आतील स्तरांचे वाटप करा. हे ग्राउंड लूप कमी करण्यास, EMI कमी करण्यास आणि उच्च-फ्रिक्वेंसी सिग्नलसाठी कमी-प्रतिबाधा परतीचा मार्ग प्रदान करण्यात मदत करते.

स्वतंत्र डिजिटल आणि ॲनालॉग ग्राउंड प्लेन:

डिझाइनमध्ये डिजिटल आणि ॲनालॉग विभाग असल्यास, प्रत्येक विभागासाठी स्वतंत्र ग्राउंड प्लेन ठेवण्याची शिफारस केली जाते. हे डिजिटल आणि ॲनालॉग विभागांमधील आवाज जोडणी कमी करण्यास मदत करते आणि सिग्नल अखंडता सुधारते.

ग्राउंड आणि पॉवर प्लेन सिग्नल प्लेनच्या जवळ ठेवा:

लूप एरिया कमी करण्यासाठी आणि आवाज पिकअप कमी करण्यासाठी ते फीड करत असलेल्या सिग्नल प्लेनच्या जवळ ग्राउंड आणि पॉवर प्लेन ठेवा.

पॉवर प्लेनसाठी एकाधिक मार्ग वापरा:

पॉवर प्लेनला समान रीतीने वितरीत करण्यासाठी आणि पॉवर प्लेन प्रतिबाधा कमी करण्यासाठी पॉवर प्लेन कनेक्ट करण्यासाठी अनेक मार्ग वापरा. हे पुरवठा व्होल्टेज थेंब कमी करण्यास मदत करते आणि पॉवर अखंडता सुधारते.

पॉवर प्लेनमध्ये अरुंद मान टाळा:

पॉवर प्लेनमध्ये अरुंद मान टाळा कारण ते सध्याच्या गर्दीला कारणीभूत ठरू शकतात आणि प्रतिकार वाढवू शकतात, परिणामी व्होल्टेज थेंब आणि पॉवर प्लेन अकार्यक्षमता. वेगवेगळ्या पॉवर प्लेन एरियामध्ये मजबूत कनेक्शन वापरा.

4.4 थर्मल पॅड आणि प्लेसमेंटद्वारे:

उष्णता प्रभावीपणे विसर्जित करण्यासाठी आणि घटकांना जास्त गरम होण्यापासून रोखण्यासाठी थर्मल पॅड आणि व्हियासची योग्य नियुक्ती महत्त्वपूर्ण आहे. थर्मल पॅडसाठी आणि 16-लेयर सर्किट बोर्डवर प्लेसमेंटद्वारे येथे काही मार्गदर्शक तत्त्वे आहेत:

उष्णता निर्माण करणाऱ्या घटकांखाली थर्मल पॅड ठेवा:

उष्णता निर्माण करणारा घटक (जसे की पॉवर ॲम्प्लिफायर किंवा हाय-पॉवर IC) ओळखा आणि थर्मल पॅड थेट त्याच्या खाली ठेवा. हे थर्मल पॅड अंतर्गत थर्मल लेयरमध्ये उष्णता हस्तांतरित करण्यासाठी थेट थर्मल मार्ग प्रदान करतात.

उष्णतेचा अपव्यय करण्यासाठी एकाधिक थर्मल मार्ग वापरा:

कार्यक्षम उष्णता नष्ट करण्यासाठी थर्मल स्तर आणि बाह्य स्तर जोडण्यासाठी एकाधिक थर्मल वायझ वापरा. समान उष्णता वितरण साध्य करण्यासाठी हे विया थर्मल पॅडच्या भोवती स्तब्ध पॅटर्नमध्ये ठेवता येतात.

थर्मल प्रतिबाधा आणि स्तर स्टॅकअप विचारात घ्या:

थर्मल वियास डिझाइन करताना, बोर्ड सामग्रीचा थर्मल प्रतिबाधा आणि लेयर स्टॅकअपचा विचार करा. थर्मल रेझिस्टन्स कमी करण्यासाठी आणि जास्तीत जास्त उष्णता नष्ट करण्यासाठी आकार आणि अंतराद्वारे ऑप्टिमाइझ करा.

4.5 घटक प्लेसमेंट आणि सिग्नल अखंडता:

सिग्नल अखंडता राखण्यासाठी आणि हस्तक्षेप कमी करण्यासाठी योग्य घटक प्लेसमेंट महत्त्वपूर्ण आहे. 16-लेयर सर्किट बोर्डवर घटक ठेवण्यासाठी येथे काही मार्गदर्शक तत्त्वे आहेत:

गट संबंधित घटक:

गट संबंधित घटक जे समान उपप्रणालीचा भाग आहेत किंवा मजबूत विद्युत परस्परसंवाद आहेत. हे ट्रेसची लांबी कमी करते आणि सिग्नल क्षीणन कमी करते.

हाय-स्पीड घटक जवळ ठेवा:

ट्रेस लांबी कमी करण्यासाठी आणि योग्य सिग्नल अखंडता सुनिश्चित करण्यासाठी हाय-स्पीड घटक, जसे की हाय-फ्रिक्वेंसी ऑसिलेटर किंवा मायक्रोकंट्रोलर एकमेकांच्या जवळ ठेवा.

गंभीर सिग्नलची ट्रेस लांबी कमी करा:

प्रसार विलंब आणि सिग्नल क्षीणन कमी करण्यासाठी गंभीर सिग्नलची ट्रेस लांबी कमी करा. हे घटक शक्य तितक्या जवळ ठेवा.

संवेदनशील घटक वेगळे करा:

आवाज-संवेदनशील घटक, जसे की ॲनालॉग घटक किंवा निम्न-स्तरीय सेन्सर, उच्च-शक्ती किंवा गोंगाट करणाऱ्या घटकांपासून, हस्तक्षेप कमी करण्यासाठी आणि सिग्नलची अखंडता राखण्यासाठी वेगळे करा.

डिकपलिंग कॅपेसिटर विचारात घ्या:

स्वच्छ उर्जा प्रदान करण्यासाठी आणि व्होल्टेज चढउतार कमी करण्यासाठी प्रत्येक घटकाच्या पॉवर पिनच्या शक्य तितक्या जवळ डिकपलिंग कॅपेसिटर ठेवा. हे कॅपेसिटर वीज पुरवठा स्थिर करण्यास आणि आवाज जोडणी कमी करण्यास मदत करतात.

5. स्टॅक-अप डिझाइनसाठी सिम्युलेशन आणि विश्लेषण साधने

5.1 3D मॉडेलिंग आणि सिम्युलेशन सॉफ्टवेअर:

स्टॅकअप डिझाइनसाठी 3D मॉडेलिंग आणि सिम्युलेशन सॉफ्टवेअर हे एक महत्त्वाचे साधन आहे कारण ते डिझाइनरना PCB स्टॅकअपचे आभासी प्रतिनिधित्व तयार करण्यास अनुमती देते. सॉफ्टवेअर स्तर, घटक आणि त्यांचे शारीरिक परस्परसंवाद दृश्यमान करू शकते. स्टॅकअपचे अनुकरण करून, डिझायनर संभाव्य समस्या जसे की सिग्नल क्रॉसस्टॉक, EMI आणि यांत्रिक मर्यादा ओळखू शकतात. हे घटकांच्या व्यवस्थेची पडताळणी करण्यास आणि एकूण PCB डिझाइनला अनुकूल करण्यास देखील मदत करते.

5.2 सिग्नल अखंडता विश्लेषण साधने:

पीसीबी स्टॅकअपच्या विद्युत कार्यक्षमतेचे विश्लेषण आणि ऑप्टिमाइझ करण्यासाठी सिग्नल अखंडता विश्लेषण साधने महत्त्वपूर्ण आहेत. ही साधने प्रतिबाधा नियंत्रण, सिग्नल रिफ्लेक्शन्स आणि नॉइज कपलिंगसह सिग्नल वर्तनाचे अनुकरण आणि विश्लेषण करण्यासाठी गणिती अल्गोरिदम वापरतात. सिम्युलेशन आणि विश्लेषण करून, डिझायनर डिझाईन प्रक्रियेच्या सुरुवातीला संभाव्य सिग्नल अखंडतेच्या समस्या ओळखू शकतात आणि विश्वसनीय सिग्नल ट्रांसमिशन सुनिश्चित करण्यासाठी आवश्यक समायोजन करू शकतात.

5.3 थर्मल विश्लेषण साधने:

थर्मल ॲनालिसिस टूल्स PCB चे थर्मल मॅनेजमेंटचे विश्लेषण करून आणि ऑप्टिमाइझ करून स्टॅकअप डिझाइनमध्ये महत्त्वाची भूमिका बजावतात. ही साधने स्टॅकच्या प्रत्येक थरामध्ये उष्णता नष्ट होणे आणि तापमान वितरणाचे अनुकरण करतात. पॉवर डिसिपेशन आणि उष्णता हस्तांतरण मार्गांचे अचूक मॉडेलिंग करून, डिझायनर हॉट स्पॉट्स ओळखू शकतात, तांबे थर आणि थर्मल व्हियासचे प्लेसमेंट ऑप्टिमाइझ करू शकतात आणि गंभीर घटकांचे योग्य कूलिंग सुनिश्चित करू शकतात.

5.4 उत्पादनक्षमतेसाठी डिझाइन:

उत्पादनक्षमतेसाठी डिझाइन हा स्टॅकअप डिझाइनचा एक महत्त्वाचा पैलू आहे. विविध प्रकारचे सॉफ्टवेअर टूल्स उपलब्ध आहेत जे निवडलेले स्टॅक-अप कार्यक्षमतेने तयार केले जाऊ शकतात याची खात्री करण्यात मदत करू शकतात. ही साधने साहित्याची उपलब्धता, थर जाडी, उत्पादन प्रक्रिया आणि उत्पादन खर्च यासारख्या घटकांना विचारात घेऊन इच्छित स्टॅकअप साध्य करण्याच्या व्यवहार्यतेवर अभिप्राय देतात. ते डिझायनर्सना मॅन्युफॅक्चरिंग सुलभ करण्यासाठी, विलंबाचा धोका कमी करण्यासाठी आणि उत्पन्न वाढवण्यासाठी स्टॅकिंग ऑप्टिमाइझ करण्यासाठी माहितीपूर्ण निर्णय घेण्यास मदत करतात.

6.16-लेयर पीसीबीसाठी चरण-दर-चरण डिझाइन प्रक्रिया

6.1 प्रारंभिक आवश्यकता संकलन:

या चरणात, 16-लेयर पीसीबी डिझाइनसाठी सर्व आवश्यक आवश्यकता गोळा करा. PCB ची कार्यक्षमता, आवश्यक विद्युत कार्यप्रदर्शन, यांत्रिक मर्यादा आणि कोणतेही विशिष्ट डिझाइन मार्गदर्शक तत्त्वे किंवा मानके समजून घ्या ज्यांचे पालन करणे आवश्यक आहे.

6.2 घटक वाटप आणि व्यवस्था:

आवश्यकतेनुसार, पीसीबीवर घटकांचे वाटप करा आणि त्यांची व्यवस्था निश्चित करा. सिग्नल अखंडता, थर्मल विचार आणि यांत्रिक मर्यादा यासारख्या घटकांचा विचार करा. इलेक्ट्रिकल वैशिष्ट्यांवर आधारित घटकांचे गट करा आणि हस्तक्षेप कमी करण्यासाठी आणि सिग्नल प्रवाह ऑप्टिमाइझ करण्यासाठी त्यांना धोरणात्मकपणे बोर्डवर ठेवा.

6.3 स्टॅक-अप डिझाइन आणि स्तर वितरण:

16-लेयर पीसीबीसाठी स्टॅक-अप डिझाइन निश्चित करा. योग्य सामग्री निवडण्यासाठी डायलेक्ट्रिक स्थिरता, थर्मल चालकता आणि किंमत यासारख्या घटकांचा विचार करा. इलेक्ट्रिकल आवश्यकतांनुसार सिग्नल, पॉवर आणि ग्राउंड प्लेन नियुक्त करा. संतुलित स्टॅक सुनिश्चित करण्यासाठी आणि सिग्नल अखंडता सुधारण्यासाठी ग्राउंड आणि पॉवर प्लेन सममितीय ठेवा.

6.4 सिग्नल राउटिंग आणि राउटिंग ऑप्टिमायझेशन:

या चरणात, योग्य प्रतिबाधा नियंत्रण, सिग्नल अखंडता आणि सिग्नल क्रॉसस्टॉक कमी करण्यासाठी घटकांदरम्यान सिग्नल ट्रेस रूट केले जातात. क्रिटिकल सिग्नल्सची लांबी कमी करण्यासाठी राउटिंग ऑप्टिमाइझ करा, संवेदनशील ट्रेस ओलांडणे टाळा आणि हाय-स्पीड आणि लो-स्पीड सिग्नलमधील वेगळेपणा राखा. आवश्यकतेनुसार विभेदक जोड्या आणि नियंत्रित प्रतिबाधा राउटिंग तंत्र वापरा.

6.5 इंटरलेअर कनेक्शन आणि प्लेसमेंटद्वारे:

स्तरांदरम्यान कनेक्टिंग व्हियाच्या प्लेसमेंटची योजना करा. लेयर ट्रांझिशन आणि घटक कनेक्शनवर आधारित, प्रकाराद्वारे योग्य ठरवा, जसे की छिद्र किंवा आंधळ्या छिद्राद्वारे. सिग्नल रिफ्लेक्शन्स कमी करण्यासाठी लेआउटद्वारे ऑप्टिमाइझ करा, प्रतिबाधा खंडित करा आणि PCB वर समान वितरण राखा.

6.6 अंतिम डिझाइन सत्यापन आणि अनुकरण:

उत्पादनापूर्वी, अंतिम डिझाइन सत्यापन आणि सिम्युलेशन केले जातात. सिग्नल अखंडता, उर्जा अखंडता, थर्मल वर्तन आणि उत्पादनक्षमतेसाठी PCB डिझाइनचे विश्लेषण करण्यासाठी सिम्युलेशन साधने वापरा. प्रारंभिक आवश्यकतांनुसार डिझाइनची पडताळणी करा आणि कार्यप्रदर्शन ऑप्टिमाइझ करण्यासाठी आणि उत्पादनक्षमता सुनिश्चित करण्यासाठी आवश्यक समायोजन करा.

सर्व गरजा पूर्ण झाल्या आहेत आणि संभाव्य समस्यांचे निराकरण झाले आहे याची खात्री करण्यासाठी संपूर्ण डिझाइन प्रक्रियेदरम्यान विद्युत अभियंता, यांत्रिक अभियंता आणि उत्पादन संघ यांसारख्या इतर भागधारकांशी सहयोग आणि संवाद साधा. अभिप्राय आणि सुधारणा समाविष्ट करण्यासाठी डिझाइनचे नियमितपणे पुनरावलोकन करा आणि पुनरावृत्ती करा.

7.उद्योग सर्वोत्तम पद्धती आणि केस स्टडीज

7.1 16-लेयर पीसीबी डिझाइनची यशस्वी प्रकरणे:

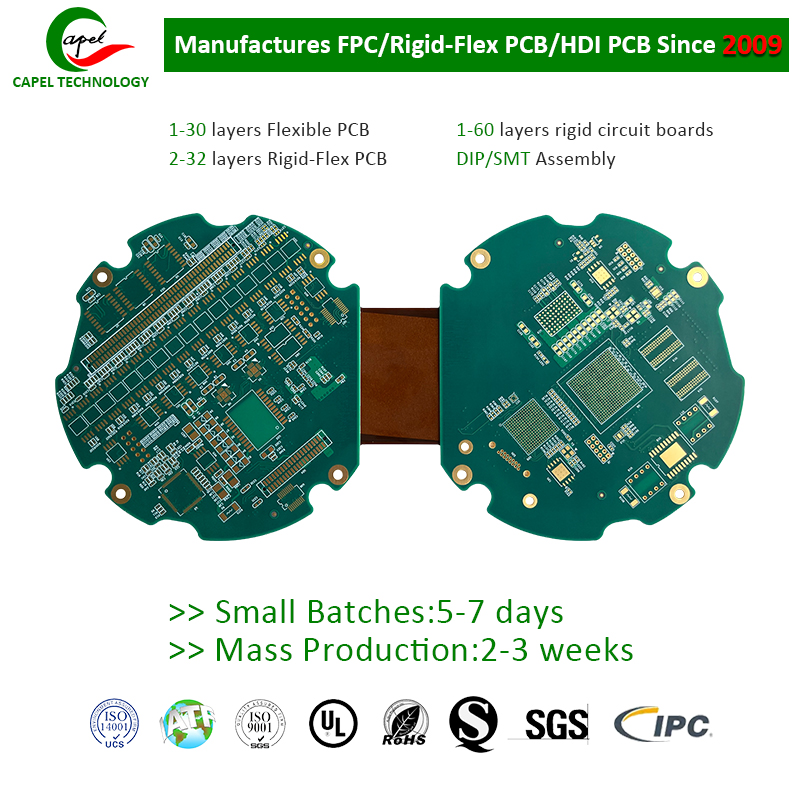

केस स्टडी 1:Shenzhen Capel Technology Co., Ltd ने हाय-स्पीड नेटवर्क उपकरणांसाठी 16-लेयर PCB यशस्वीरित्या डिझाइन केले आहे. सिग्नल अखंडता आणि उर्जा वितरणाचा काळजीपूर्वक विचार करून, ते उत्कृष्ट कार्यप्रदर्शन प्राप्त करतात आणि इलेक्ट्रोमॅग्नेटिक हस्तक्षेप कमी करतात. नियंत्रित प्रतिबाधा राउटिंग तंत्रज्ञानाचा वापर करून पूर्णतः ऑप्टिमाइझ केलेले स्टॅक-अप डिझाइन हे त्यांच्या यशाची गुरुकिल्ली आहे.

केस स्टडी 2:Shenzhen Capel Technology Co., Ltd ने जटिल वैद्यकीय उपकरणासाठी 16-लेयर PCB डिझाइन केले आहे. पृष्ठभाग माउंट आणि थ्रू-होल घटकांच्या संयोजनाचा वापर करून, त्यांनी एक संक्षिप्त परंतु शक्तिशाली डिझाइन प्राप्त केले. काळजीपूर्वक घटक प्लेसमेंट आणि कार्यक्षम राउटिंग उत्कृष्ट सिग्नल अखंडता आणि विश्वासार्हता सुनिश्चित करते.

७.२ अपयशांपासून शिका आणि अडचणी टाळा:

केस स्टडी 1:काही पीसीबी उत्पादकांना संप्रेषण उपकरणांच्या 16-लेयर पीसीबी डिझाइनमध्ये सिग्नल अखंडतेच्या समस्या आल्या. अयशस्वी होण्याचे कारण म्हणजे प्रतिबाधा नियंत्रणाचा अपुरा विचार आणि योग्य ग्राउंड प्लेन वितरणाचा अभाव. शिकलेला धडा म्हणजे सिग्नल अखंडतेच्या आवश्यकतांचे काळजीपूर्वक विश्लेषण करणे आणि कठोर प्रतिबाधा नियंत्रण डिझाइन मार्गदर्शक तत्त्वांची अंमलबजावणी करणे.

केस स्टडी 2:काही पीसीबी निर्मात्यांना त्याच्या 16-लेयर पीसीबीसह डिझाइनच्या जटिलतेमुळे उत्पादन आव्हानांना सामोरे जावे लागले. अंध विया आणि घनतेने पॅक केलेल्या घटकांच्या अतिवापरामुळे उत्पादन आणि असेंब्लीमध्ये अडचणी येतात. निवडलेल्या PCB निर्मात्याच्या क्षमतेनुसार डिझाइनची जटिलता आणि उत्पादनक्षमता यांच्यात संतुलन राखणे हा शिकलेला धडा आहे.

16-लेयर पीसीबी डिझाईनमध्ये अडचणी आणि त्रुटी टाळण्यासाठी, हे करणे महत्वाचे आहे:

अ. डिझाइनच्या गरजा आणि मर्यादा पूर्णपणे समजून घ्या.

b. स्टॅक केलेले कॉन्फिगरेशन जे सिग्नल अखंडता आणि पॉवर वितरण ऑप्टिमाइझ करतात. c. कार्यप्रदर्शन ऑप्टिमाइझ करण्यासाठी आणि उत्पादन सुलभ करण्यासाठी घटकांचे काळजीपूर्वक वितरण आणि व्यवस्था करा.

d. योग्य राउटिंग तंत्रांची खात्री करा, जसे की प्रतिबाधा नियंत्रित करणे आणि ब्लाइंड वायसचा जास्त वापर टाळणे.

e. इलेक्ट्रिकल आणि मेकॅनिकल इंजिनीअर्स आणि मॅन्युफॅक्चरिंग टीम्ससह डिझाइन प्रक्रियेत सहभागी असलेल्या सर्व भागधारकांशी सहयोग आणि प्रभावीपणे संवाद साधा.

f. उत्पादनापूर्वी संभाव्य समस्या ओळखण्यासाठी आणि दुरुस्त करण्यासाठी सर्वसमावेशक डिझाइन सत्यापन आणि सिम्युलेशन करा.

पोस्ट वेळ: सप्टेंबर-26-2023

मागे